黄乐天

![]()

开通时间:..

最后更新时间:..

2026年考研主要招收“湖州专项”的全日制和非全日制研究生。“湖州专项”无论何种形式均享受湖州市提供的免费住宿、生活补贴、学费报销等政策,对报考同学较为友好。具体情况咨询可联系邮箱:huanglt@uestc.edu.cn

联系前建议认真阅读主页上有关团队的相关介绍事宜,以免发生误会浪费双方的时间。

IEEE Senior Member,电子科技大学长三角研究院(湖州)集成电路与系统研究中心副主任。

长期从事算力芯片相关研究,主要包括专用微处理器与领域专用片上系统、并行计算机互连子系统与互连桥接芯片、存内计算芯片与存算一体化系统、计算机芯片可靠性/可测性设计、面向通信与信息处理的专用加速器等方面的工作,承担自然基金重点研究计划项目、国家科技重点专项项目、江苏省“揭榜挂帅”等国家级、省部级项目多项,与国内知名芯片设计企业和头部科研院所长期开展科研合作。先后基于PowerPC、MIPS、ALPHA、ARM、SPARC、RISC-V等不同指令集的设计和验证过多款专用系统级芯片。团队研究生毕业后主要在阿里巴巴达摩院、平头哥、地平线、海思、复旦微电子、安谋科技、芯原、安路等专业芯片设计公司从事系统级大算力芯片设计工作,也有部分同学进入华为、中兴、海康等系统设计公司从事软硬件协同设计、底层软件开发、FPGA逻辑设计等相关工作。

所指导的队伍获得“华为杯”第五届中国研究生创芯大赛决赛一等奖,队伍在最终决赛中的路演视频如下:

由于算力芯片研发投入的资金和人力巨大,团队采取和产业界头部企业以及重点科研院所合作的模式开展科研。目前团队的主要科研合作对象都分布在长三角地区,团队学生在研一结束以后将在湖州、无锡、南京等地开展课题。由于课题的特殊性,无法在成都开展。如果报考电子科技大学研究生的目的之一是因为“喜欢成都”或者说“返回四川”的同学建议不要报考本团队。

由于本团队的研究方向特殊,属于计算机与集成电路的交叉方向,与传统概念上所谓的“数字集成电路设计”有较大的区别。为避免盲目选择对师生双方今后3年相互带来的痛苦,对于本团队研究方向感兴趣的同学建议先观看B站伯克利大学EECS151课程:https://www.bilibili.com/video/BV1eu411r7Y3?spm_id_from=333.337.search-card.all.click&vd_source=e820315228995be80517e285293e0215

从而判断自己的兴趣以及基础是否适合本团队。

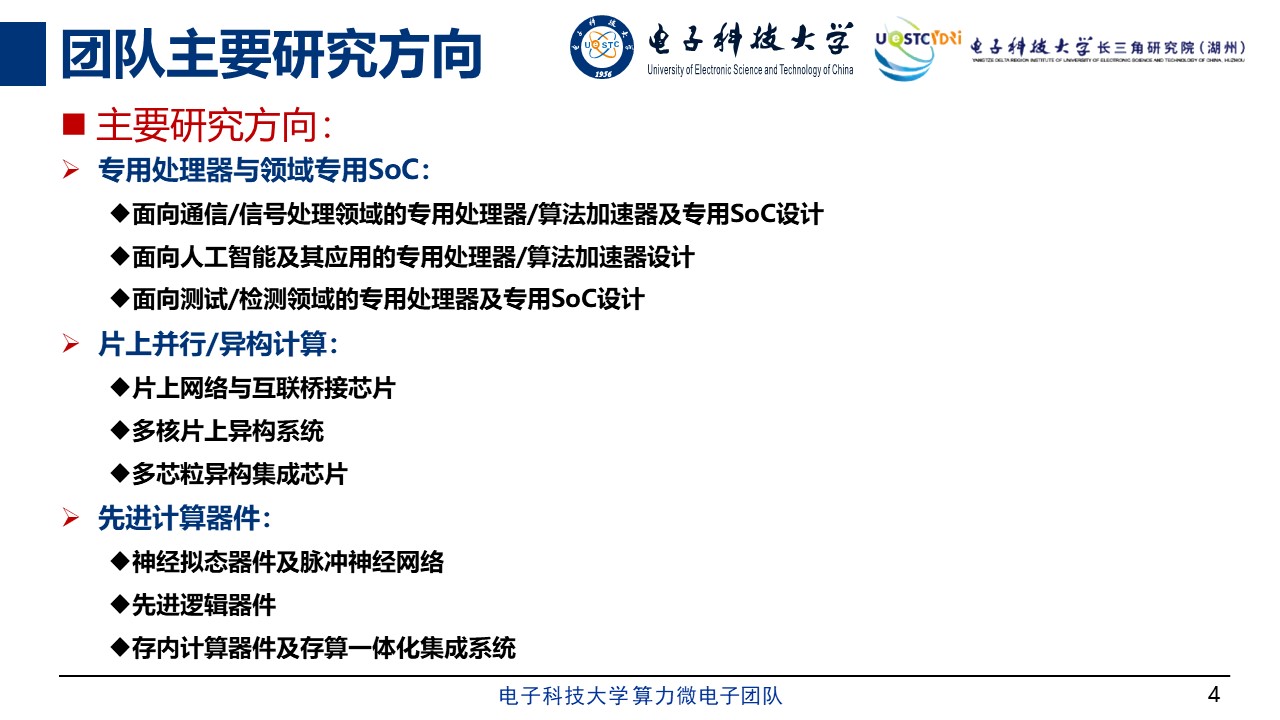

本团队主要研究方向详细介绍如下:

团队以“立足器件、面向应用、始于电路、终于系统”的思路长期从事通信/信息处理、计算机系统与先进微电子技术交叉领域的研究。与头部IC设计公司、国内重点科研院所等长期合作,着力突破算力芯片设计相关的各项关键技术,形成新的设计方法、设计流程、关键IP核以及芯片原型,服务于国家算力基础设施能力提升的重大战略。

团队目前形成了三个具体的研究方向,主要包括:专用处理器与领域专用SoC、片上并行/异构计算、先进计算器件,三个方向相互支撑、交叉融合。

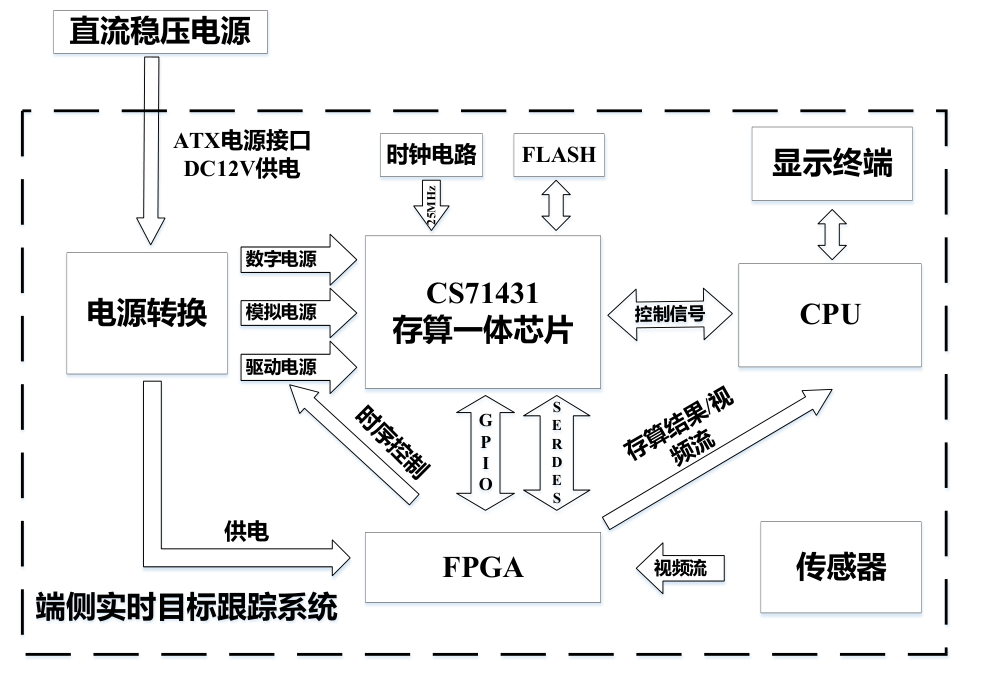

领域专用SoC典型项目:存算一体化智算芯片及系统

联合国内算力芯片领域头部研制单位研制基于Flash工艺的存算一体化智算芯片,基于该芯片通过FPGA、CPU等常规算力器件的异构集成,构造面向图像信息智能检测、分类、识别的智能微系统组件。峰值算力超过110TOPS@INT8,已实现多个示范性应用。

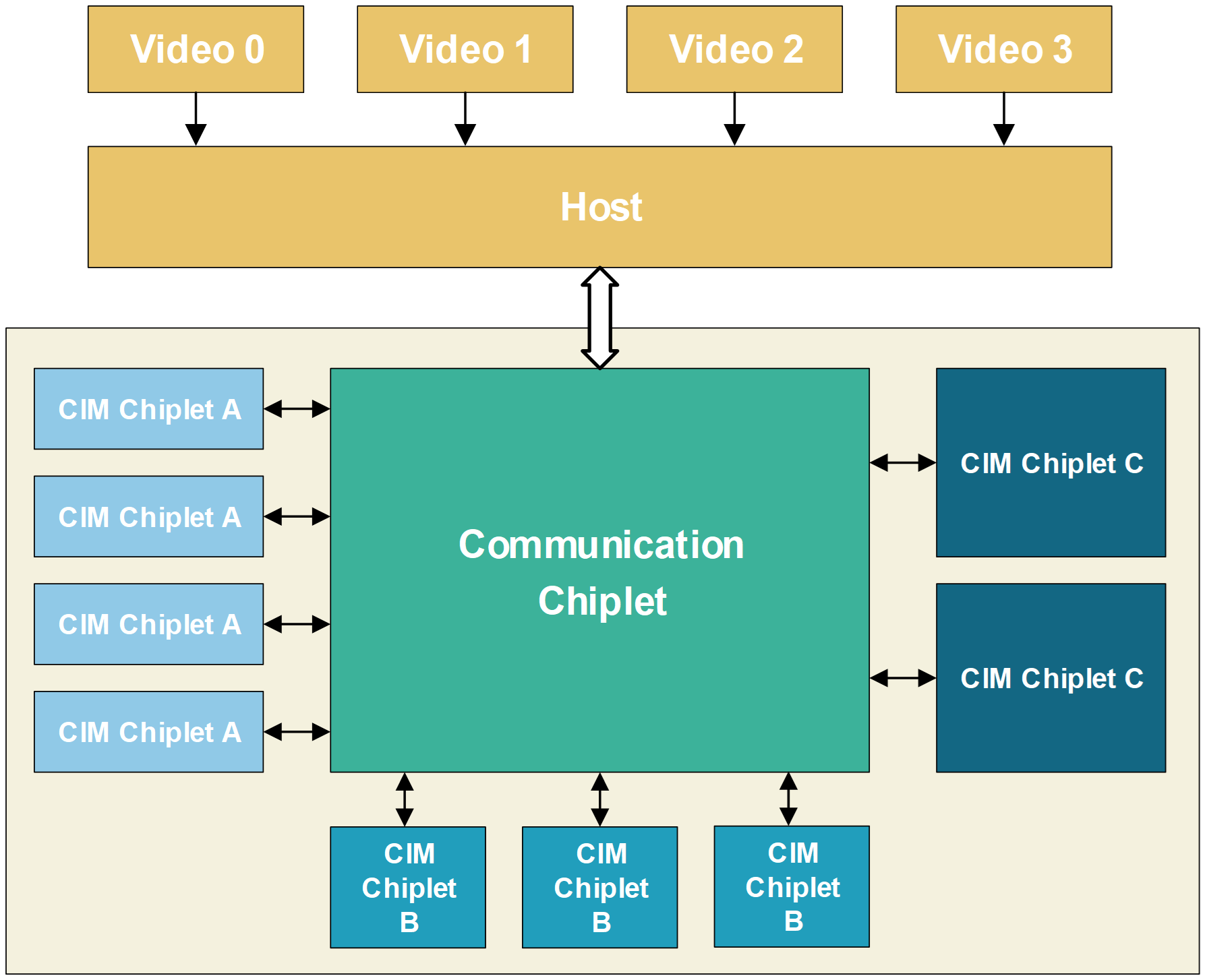

片上并行/异构计算典型项目:多芯粒异构集成芯片设计

为国内算力芯片领域头部企业设计的多芯粒异构集成方案。通过设计互联通信芯粒实现了不同异构芯粒之间的数据交互,最终基于2.5D集成方案实现了大算力异构集成芯片。

团队目前规模不大,因此每个同学负担的科研任务量较大,每一个具体的研究点每届通常只有1-2名(1名保送+1名考研)同学参与。因此需要同学们综合能力较为全面、自我组织和管理能力较强,否则可能因难以推进项目造成自身压力过大等困扰。请报考前对于以后的研究生生活和工作状态有初步的预期以后再考虑是否报考。一般情况下团队将事务性/基础性的工作(焊板子、调电路、做后端、写驱动)等工作外协解决,减少同学们的精力消耗,让研究生期间同学们的主要精力集中于“定义关键问题、提出解决方案、配合方案实施”等创新性工作上

再次说明:目前我们团队的主要科研合作在长三角地区,研一结束以后很大概率在湖州、无锡、南京等地开展课题。由于课题的特殊性,无法在成都开展。如果报考电子科技大学研究生的目的之一是因为“喜欢成都”或者说“返回四川”的同学建议不要报考。

团队的研究生毕业后主要在平头哥、海思、复旦微电子、芯源、安路科技等专业IC设计公司从事系统级芯片设计工作和华为、中兴、海康等系统设计公司从事软硬件协同设计相关工作。以下为近几年团队毕业生来源及毕业后的去向。

对团队有兴趣的同学可以通过以下方式联系,对于片上系统、FPGA等团队从事的科研、教学工作由兴趣的同学也可以通过以下方式获取学习资源。

通讯/办公地址 : 3a375438a1df344fa5cb191998dff9ae5b5e4af74faa301997c8858bb92cf1f19ce3c7332013a79faadaaf3ce6e4937f01024f5754a90e1af7069386883b1c017a3fbe4b4ae81dea5ab7ad7bac125205c90a4a843e1e54647bd76b7c0acfa49ac391301c274e12aae0cd6b3b9002117f476e4f5d64dc36f8e170af7d62d040aa

邮箱 : 8430113f2fbf5795b32872ff69b9dc10255ab5e516898c7f202fda502353fd56264c8a14cb61c82492ff9b10b53b9f85ec0252aace1750b8f565acc8d8f68c505bb6e219c6c6bc08fa1d60cfe15041db21c40d9f10e926586bf6bdb367cfcc2694205977845a39feaad8412c347794c636cafc472ae52e24756445d6a1b13a44

电子科技大学

工学学士学位

电子科技大学

工学硕士学位

电子科技大学

工学博士学位

2024.1 -- 至今

电子科技大学 集成电路科学与工程学院

2017.12 -- 2023.12

电子科技大学 电子科学与工程学院(示范性微电子学院) 副教授

2016.9 -- 2017.11

电子科技大学微电子与固体电子学院 专任教师

2013.9 -- 2014.9

瑞典皇家工学院 访问学者

2009.7 -- 2016.8

电子科技大学通信与信息工程学院 专任教师

2019.10 -- 至今

中国计算机学会(CCF)集成电路专业委员会执行委员

2017.9 -- 至今

西南地区高校电子线路、电子技术研究会理事

2017.11 -- 至今

中国计算机学会(CCF)嵌入式系统专委会委员