|

个人信息Personal Information

研究员 博士生导师

性别:男

学历:博士研究生毕业

学位:工学博士学位

入职时间:2021-04-01

学科:微电子学与固体电子学

办公地点:电子科技大学清水河校区成电国际创新中心B435B

-

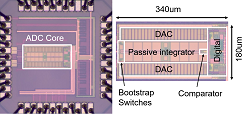

1. 基于电容叠加与缓冲的新型积分器及噪声整形SAR ADC芯片 [ISSCC 2021]

The prior noise-shaping SAR ADCs rely on closed-loop charge transferring or passive charge sharing. The former is power consuming, and the latter suffers from limited noise suppression or PVT variation. In this work, we propose an efficient new integrator technique. This integrator doesn’t require any amplifier, thus is power efficient and PVT robust. It also avoids the large signal attenuation caused by passive charge sharing, therefore it can build a noise-shaping SAR ADC with sharp NTF and strong noise suppression. It has low hardware complexity, and is easy for high order extension. A 4th-order noise-shaping SAR ADC is realized based on this integrator. It measures 93dB SNDR over 250kHz bandwidth with 340uW power consumption, leading to a schreier FoM of 182dB.

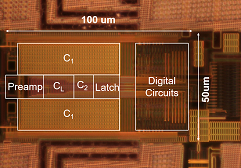

2. 实现采样kT/C噪声抵消的ADC芯片 [ISSCC 2020, JSSC 2020]

As any ADC with a front-end S/H, SAR ADC suffers from a fundamental SNR challenge: its sampling kT/C noise. To satisfy the SNR requirement, the input capacitor has to be sufficiently large. This work presents a SAR ADC with a kT/C noise cancellation technique. It enables the substantial reduction of ADC input capacitance but without large kT/C noise penalty, greatly relaxing the requirement for the ADC input driver and reference buffer.

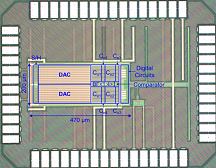

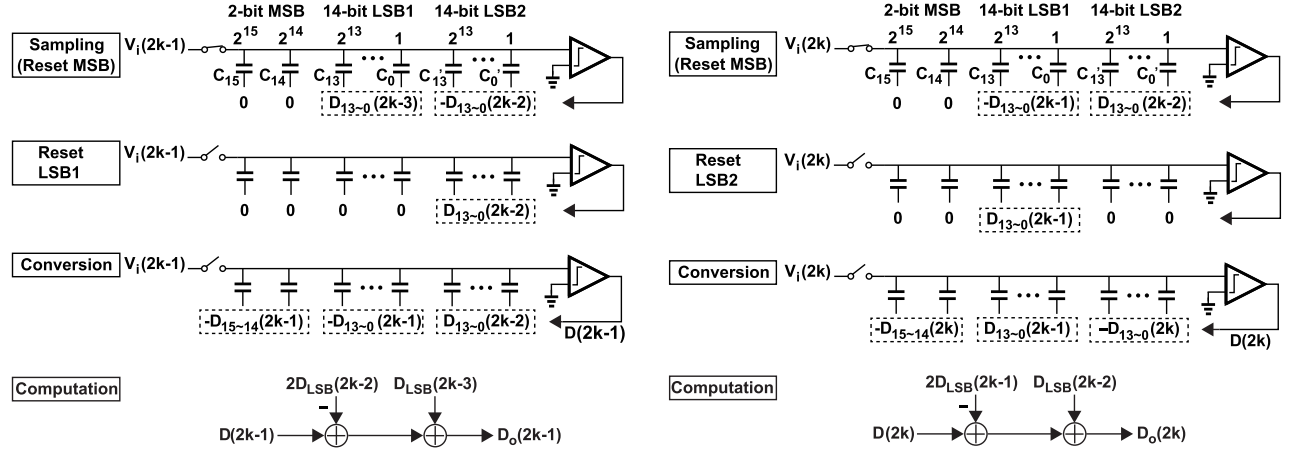

3. 实现无源增益噪声整形和二阶失配误差整形的SAR ADC芯片 [ISSCC 2020-1, JSSC 2021]

This work presents a 90dB-SNDR passive NS SAR with 2nd-order mismatch error shaping. It has an efficient architecture that removes the residue sampling and realizes 4× passive gain, leading to reduced total kT/C and comparator noise. Moreover, it realizes 2nd-order MES that is tone-free and supports full input range.

4. 集成NS-SAR量化器的CT-DT混合结构ΔΣ ADC [VLSI 2018, JSSC 2019]

This work presents a compact and power efficient third-order continuous-time (CT) Delta-Sigma (∆Σ) ADC with a single OTA. A 4-bit second-order fully passive noise-shaping SAR ADC is employed as the quantizer while inherently provides two additional noise shaping orders.

5. 高阶失配误差整形与数字预测的理论研究工作 [TCAS-I 2019]

Device mismatch is a key concern for high-resolution data converters. This work presents a comprehensive study of the error-feedback (EF)-based mismatch error shaping (MES) technique. EF MES overcomes the key challenge of the classic dynamic element matching-based MES whose complexity grows exponentially with the number of bits; however, the prior EF MES comes with the limitations of limited shaping capability and reduced dynamic range. This paper demonstrates how to perform more advanced EF MES for various types of data converters. Moreover, this paper also proposes the use of digital prediction to address the dynamic range loss issue.

- 暂无内容

- 暂无内容